I’ve looked into a lot of the internals of the Loxone Miniserver (the CAN bus protocols, the SD card file system, etc) and written it down with a lot of sample code at https://github.com/sarnau/Inside-The-Loxone-Miniserver. For the ambitious i’ve also provided an STM32 ARM implementation of the Loxone Link/Loxone Tree protocol for a lot of hardware at https://github.com/sarnau/LoxLink

Category: Reverse Engineering

Communication protocol of the Proteus EcoMeter TEK603

The receiver device has a USB port, which has a CP2102 USB<->RS232 converter. With 115200 baud, 8N1 it is possible to communicate with the device.

Package format

All data to or from the device is transmitted as a package.

- 2 byte header (‘SI’ = 0x53,0x49)

- 2 byte length of the complete package (16 bit, big-endian)

- 1 byte command (1: data send to the device, 2: data received from the device)

-

1 byte flags:

- bit 0: set the clock (hour/minutes/seconds) in the device on upload

- bit 1: force reset the device (set before an update of the device)

- bit 2: a non-empty payload is send to the device

- bit 3: force recalculate the device (set on upload after changing the Sensor Offset, Outlet Height or the lookup table)

- bit 4: live data received from the device

- bit 5: n/a

- bit 6: n/a

- bit 7: n/a

-

1 byte hour – used to transmit the current time to the device

- 1 byte minutes

-

1 byte seconds

-

2 byte eeprom start (16 bit, big-endian) – unused in live data

-

2 byte eeprom end (16 bit, big-endian)

-

n bytes payload

-

2 byte CRC16 (16 bit, big-endian)

The app never always read more than about 800 bytes of data at once, e.g. reading the history is done in 4 reads:

- 0x0000..0x0031 Header

- 0x0032..0x0289 Offsets

- 0x028a..0x03e5 This 365 entry history

- 0x03e6..0x06d0 ..continuation of the history

Live data

With an open connection and without significant change of the fluid level, the current level is send every 30/60 minutes (water/oil) to the computer. There seems to be no way to request it. Because the wireless transmitter only sends the data in that frequency, it probably makes very little sense.

If the level changes (refilling the tank) it updates much more often.

Live data has the following payload:

- 1 byte temperature in Fahrenheit + 40. The get the temperature in Celcius you need to calculate it like this =>

temperatureC = ((temperatureF - 40 - 32) / 1.8) - 2 byte sensor level in cm (16-bit, big-endian)

- 2 byte usable capacity in l (16-bit, big-endian)

- 2 byte full capacity of the tank in l (16-bit, big-endian)

EEPROM content

The EEPROM has three distinct areas:

- Header and configuration

- tank air space table (liters of tank volume based on the level above the fluid (0..300cm))

- 365 days of average usage – a round-robin buffer

Header and configuration

If there is no description, the value is unknown.

- 0x00: 0xcc (204) Magic byte, always checked to test the communication with the device.

- 0x01: 0x18 0x3D 0xff 0xca

- 0x05: 0x03 Type of the tank A..D (0..3) The tank offset table is calculated by the device based on the setting (A-C). If the table is modified via a computer, the type is set to D (3).

- 0x06: 0x0096 Height of the tank in cm (here: 150)

tankHeight - 0x08: 0x0048 Width of the tank? (Probably entered during configuration)

- 0x0a: 0x0064 Height of the tank without the rounding? (Probably entered during configuration)

- 0x0c: 0x2710 Volume of the tank (10000l)

- 0x0e: 0x01

-

0x0f: 0x00

-

0x10: 0x00

- 0x11: 0x00 0/1 Alarm Off/On

- 0x12: 0x01

- 0x13: 0x002d 45 Index to todays entry in the history

historyIndex. Because the history starts yesterday, you need to start with the next index for yesterday. - 0x15: 0x02

- 0x16: 0x00

- 0x17: 0x43

- 0x18: 0x00

- 0x19: 0x34

- 0x1a: 0x00

- 0x1b: 0x3a

- 0x1c: 0x05db (16-bit, big-endian, cost of fuel: 0.00 – 15.00 currency/l)

- 0x1e: 0x00

-

0x1f: 0x00

-

0x20: 0x00

- 0x21: 0x00

- 0x22: 0x00

- 0x23: 0x00

- 0x24: 0x00

- 0x25: 0x00

- 0x26: 0x00

- 0x27: 0x00 Sensor Offset

sensorOffsetin cm (0..70cm) - 0x28: 0x08 Outlet Height

outletHeightin cm (0..70cm) - 0x29: 0x1b

- 0x2a: 0x00

- 0x2b: 0x03

- 0x2c: 0x1c

- 0x2d: 0x00

- 0x2e: 0x94

- 0x2f: 0x00

- 0x30: 0x00 0xDD

Tank Air Space Table tankAirSpaceTable

The distance from the bottom of the transmitter to the top of the fluid. The table has one value per cm tankHeight – up to 300cm is supported. If the distance between the top and the transmitter is 0, the capacity is the maximum value. This table is calculated by the tank type A-C automatically, but can be customized to match any shape (tank type D). It is used to convert the level in cm into liter.

The outletHeight is an offset that is added to the level to return the volume of the tank. It can be used to define a reserve.

History

The history table is 365 entries large. Each entry is 3 bytes. It is a cyclic buffer with an index pointer in the header pointing at todays position. To go into the past increment the index and wrap around at 365 till you hit today again.

The 3 bytes have this format: 0xaa 0xbc 0xcc

- ‘aa’ changes up/down a bit, but it is also not clear what it means.

- ‘b’ also unknown. I’ve only seen values of 1 or 2 for it.

- ‘ccc’ is the average oil usage in 0,1l on that day (divide by 10 to get liters). 0 if there was no oil used on a day.

The level of the tank based on todays usage is estimated in liters as follows:

usage = ccc / 10 - sensorOffset

lowValue = tankAirTable[(int)usage]

highValue = tankAirTable[(int)usage+1]

usage = highValue + (lowValue - highValue) * (1 - (usage - (int)usage))

usage = usage - tankAirTable[tankHeight - outletHeight]

Loxone MicroSD Cards

Loxone states the following on their website:

Use only Loxone SD cards for the Miniserver. All SD cards have their own CPU which manages the flash memory. For optimum performance, Loxone OS accesses many low-level functions of the SD card, unlike, for example, a digital camera.

Wow, this is exciting! What mystery low level functions are they using? Time to find out.

The server ships with a 4GB Micro SD Card, which is of the SDHC type.

SD cards exists in many different varieties, but have to follow the specifications from the SD Group. This includes the communication on the bit level, as well as how commands are executed. However, there are options to have custom commands or at least non-mandatory commands. It is also possible to only support a subset of commands for a manufacturer, if they supply specific SD cards. Loxone could do that, but it is not probable, just because it makes it really hard for them to switch vendors for their SD cards, if prices and or availability changes. You don’t want to release an update to the Miniserver for different types of SD cards.

As I already looked at the mainboard of the Miniserver, it seems the CPU is talking directly to the SD card. That is not a surprise, considering that even Arduinos can do that easily. The Miniserver does that with the help of some gate logic, probably for buffering. I didn’t really care to look into the exact implementation details too much here.

Considering that the physical communication is standardized and that the actual firmware is read from the SD card by the boot code from the flash memory, I don’t expect too much special code for reading. And I am correct: the initialization phase for the SD card seems to follow the specification from the SD Group perfectly and can detect all types of SD cards up to SDHC.

The detailed information collected during initialization about the card can be requested from Loxone Config via “Detailed Device Info”:

SD-Test: SD performance read=403kB/s write=345kB/s no error (0 0), ManufactorerID 2 Date 2016/3 CardType 2 Blocksize 512 Erase 0 MaxtransferRate 25000000 RWfactor 2 ReadSpeed 22222222Hz WriteSpeed 22222222Hz MaxReadCurrentVDDmin 3 MaxReadCurrentVDDmax 5 MaxWriteCurrentVDDmin 5 MaxWriteCurrentVDDmax 1 Usage:1.71%

What does these things mean?

- read = measured data read performance in kB/s after 1MB of reading a test file

- write = measured data read performance in kB/s after 1MB of writing a test file

- no error (0 0) = number of errors with this SD card (first number/error code = 0: no error, 1: read error, 2: verify error, second number: number of errors)

- ManufactorerID (yes, that is probably an original Austrian typo) = The manufacturer of the card. The ID is assigned by the SD Group.

- Date = Manufacturing date of the card

- CardType = 0 = unknown, 1 = SDv2, 2 = SDHC, 3 = SDv1 – detected during initialization

- Blocksize = 512 bytes (I think it this is true for all cards)

- Erase = DATA_STAT_AFTER_ERASE from the SCR register. Defines the data status after erase.

- MaxtransferRate = TRAN_SPEED from the CSD register. Maximum data transfer rate per one data line in bit/s

- RWfactor = R2W_FACTOR from CSD register (0 = 1, 1 = 2 (write half as fast as read) , 2 = 4, 3 = 8, 4 = 16, 5 = 32)

- ReadSpeed = 133333333 / (2 * ((133333333 / (2 * MaxtransferRate)) + 1))

- WriteSpeed = 133333333 / (2 * ((133333333 / (2 * MaxtransferRate)) + 1)) (always identical to ReadSpeed)

- MaxReadCurrentVDDmin = VDD_R_CURR_MIN from CSD register (0=0.5mA; 1=1mA; 2=5mA; 3=10mA; 4=25mA; 5=35mA; 6=60mA; 7=100mA)

- MaxReadCurrentVDDmax = VDD_R_CURR_MAX from CSD register (0=1mA; 1=5mA; 2=10mA; 3=25mA; 4=35mA; 5=45mA; 6=80mA; 7=200mA)

- MaxWriteCurrentVDDmin = VDD_W_CURR_MIN from CSD register (0=0.5mA; 1=1mA; 2=5mA; 3=10mA; 4=25mA; 5=35mA; 6=60mA; 7=100mA)

- MaxWriteCurrentVDDmax = VDD_W_CURR_MAX from CSD register (0=1mA; 1=5mA; 2=10mA; 3=25mA; 4=35mA; 5=45mA; 6=80mA; 7=200mA)

- Usage = How much of the SD card is used by data

The maximum supported capacity is 16GB, so do not use larger ones.

All the technical information is reported from the SD card and only for information. After initialization, what else does the Miniserver do to communicate to the card?

- Reading blocks via Block Read (CMD17)

- Writing blocks via Block Write (CMD18)

- Erasing blocks by simply writing empty blocks

- Repair after errors: power cycle the SD card and reinitialize the card (just as when the server is booting)

There are three different types of SD Card errors possible:

- Hardware errors during reading/writing. They occur within the low-level communication with the SD card itself. In this case a repair is automatically tried.

- CRC error. The Loxone filesystem has checksums over each block. If they don’t match, it is an error – this could potentially happen, if the SD card is defect. But the software also tries to do a repair.

- SD card is full. The Miniserver tries to write data, but there is no more space on the SD card.

The Miniserver only uses mandatory commands, this means every single SD card in the market has to implement them. Therefore any SD card from any good manufacturer should work just fine in the Miniserver. That said: there are Chinese manufacturers who sell SD cards with a limited actual capacity (e.g. 2GB) but which identify themselves as e.g. 16GB cards. This will result in data loss!

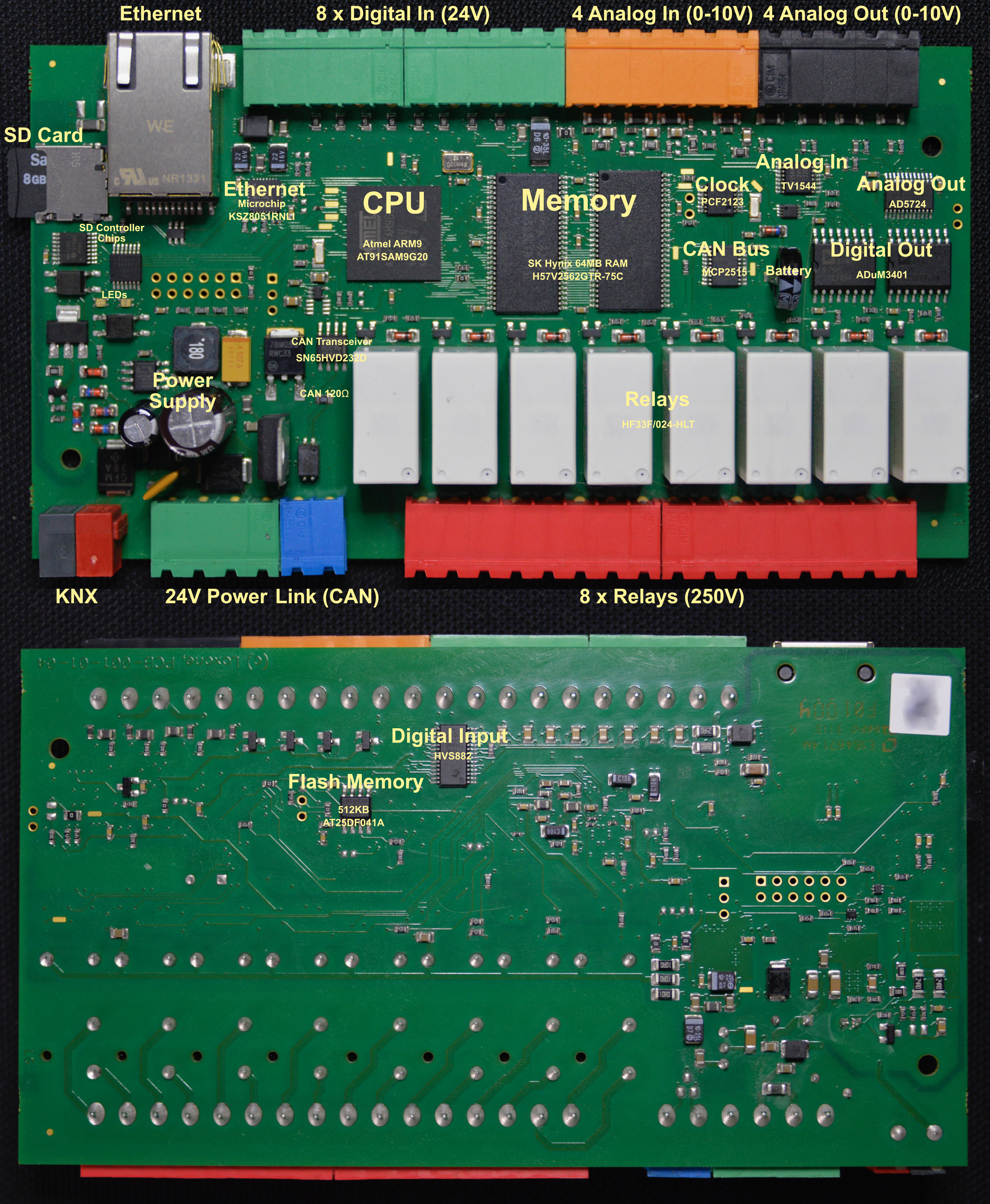

Inside the Loxone Miniserver

I’d like to explain some technical details of the Loxone Miniserver. The Miniserver (as well as all extensions) are ARM based, just like all modern mobile phones. It is clocked at just 8MHz.

The Miniserver is ARM based. The CPU is booting from a 512kb flash memory. This code then loads the actual operating system from the SD Card into the additional 64MB of memory and executes it from there.

CPU, Flash Memory, SRAM

The CPU is an Atmel AT91SAM9G20 from Microchip. It is a 3,3V 400MHz ARM926 with 32kb internal SRAM and 64kb internal ROM. It is paired with a serial interface Flash memory (AT25DF041A from Adesto Technologies), which is updatable by Loxone – it is one of two chips mounted on the back of the board. This flash memory also contains non-volatile memory used by the Miniserver, like encryption keys, which are not stored on the SD card. The other important chips are two SD RAM chips (H57V2562GTR from SK Hynix) as additional memory with 256MBit each adding another 64MB of memory.

Ethernet

The Ethernet is connected with another Chip from Microchip, the KSZ8051RNL1. Which is a 10BASE-T/100BASE-TX Automotive Physical Layer Transceiver. It doesn’t offer a lot, so most of the load for the different protocols TCP/IP and UDP, ARP, DHCP, etc. are all handled by the CPU.

SD Card

The SD Card is accessed with some logic gate directly. Nothing special here.

RTC Clock

The Miniserver has a battery backed CMOS Real-Time Clock (RTC) via a PCF2123 from NXP Semiconductors. This allows the system to run without an internet connection, while still having a valid time. During boot it is set if possible by testing various NTP servers.

Relays / Digital Out

The Relays are HF33024-HLT, which are isolated from the CPU by two ADuM3401 from Analog Devices.

Analog Out

The Analog Out are driven by a AD5724 also from Analog Devices, which is a a complete, quad, 12-/14-/16-Bit, serial input, unipolar/bipolar voltage output DAC. They are driven to have a 10V output range with a 12-bit resolution.

Analog In

The Analog Ins are driving by a TV1544 from Texas Instruments. It is a CMOS 10-bit switched-capacitor successive-approximation (SAR) analog-to-digital (A/D) converter.

Digital In

The digital inputs are read by a HVS882 from Texas Instruments. It is an 8-channel digital input serializer, which can handle up to 34V at the inputs with a flexible current limiter – it therefore also protects the CPU from damage. This is the other chip, which is mounted on the back of the board.

Loxone Link

The Loxone Link bus is standard CAN bus connected via a CAN controller (MCP2515, also Microchip) to the CPU. It is using a standard CAN Transceiver (SN65HVD232D from Texas Instruments) to protected the Miniserver from defects on the bus. The Miniserver also has a 120Ω resistor built-in, so it has to be on the end of the CAN bus. The CAN bus is clocked at 125kHz (which allows up to 500m of cable length for the Loxone Link bus).

All packages are using the extended frame format. The identifier is therefore always 29-bit (0…0x1FFFFFFF) and the data package is always 8 bytes long. Any CAN bus monitor hardware will work just fine with the Loxone Link bus.

The Loxone Link bus is a strict Master-Slave bus. The Miniserver as the master talks to the extensions, the extensions send data to the Miniserver. Extensions never talk to each other. The Miniserver can either multicast to all extensions or to specific extensions via direct commands. In the update case, it can send the update to all extensions of a certain type at the same time.

Photo with Labels of the Mainboard

Loxone UDP/HTTP Command Parser Syntax

Loxone can parse incoming data e.g. via UDP/HTTP to detect variables. I found their documentation not really good. It feels like it is almost an art to setup these parse strings, while it is actually quite simple.

The string is searched in the incoming data stream. If the full string is detected, it succeeds and returns the value (0.0 being the default). If it didn’t match the whole pattern within the stream, it resets and continues again to parse the data. Only if the whole string was parsed fully, will the matching stop.

Possible characters in the parse string

Matching individual characters

- 7-bit ASCII characters: they are taken as-is and need to match

- \\ matches a single \ (0x5C)

- \n matches a LF (0x0A)

- \r matches a CR (0x0D)

- \t matches a TAB (0x09)

- \xAB match a hex byte AB. This allows matching non-ASCII characters. \xAB would match 0xAB.

- \a match a letter (A-Z, a-z)

- \b match a TAB or space (0x09, 0x20)

- \m match a letter or digit (A-Z, a-z, 0-9)

- \d match a digit (0-9)

- \. matches any byte (= skips/ignores one byte)

Matching multiple characters

- \# match any number digits and . , or -. This should match a regular floating point number and continue after the number.

- \w match any number of letters and digits (A-Z, a-z, 0-9). This should match a word and continue after that word.

- \s123 skips/ignores 123 bytes in the incoming data stream. All digits following \s are using to build a number, the value can be really large – more than is ever needed.

Searching

-

\iXXX\i searches the string XXX and continues after that string with matching. The string can have standard UNIX control characters (\a, \b, \f, \n, \r, \t, \v plus the hex extension: \xAB).

Storing a value

The returned value is always a 64-bit floating point number, which can result in rounding issues for certain integer values.

- \1…\8 stores the following byte as part of a 64-bit binary integer result. \1 is the LSB, \8 is the MSB. Sign-extension can be applied.

- \h (hex value) stores the following ASCII-hex data (0-9, a-f, A-F) as a 32-bit MSB integer result. First invalid character ends the value. The value is returned as-is, no sign extension is applied.

- \v (value) stores a value created from ASCII characters. Any number of spaces before the values are ignored. Then the optional sign (+ or -) can follow, plus more spaces. A &nbps; is ignored after the sign as well. The number is any number of digits (0-9) followed by (, or .) plus more digits. Then an exponent (E or e) can follow plus more digits. The first character not matching the described number will end the value. The resulting number is obviously a floating point value.

- If \f (factor?) is part of the search term, the value will always be 0.0. This feels like a bug in the code and \f was probably thought to be a multiplication factor for the incoming value.

It is possible to have several \h and \v in the search pattern. Only the last one will be used. Same with \1, etc. If more than one \1 occurs, the first one will be ignored as well.

Loxone LoxCC Fileentpacker

Hi,

Here a quick Gist to uncompress a Loxone LoxCC file in Python: https://gist.github.com/sarnau/e14ff9fe081611782a3f3cb2e2c2bacd

Charge Master 2016 Serial Protocol

Charge Master 2016 Serial Protocol

The Voltcraft (Conrad) Charge Master 2016 has a completely different protocol from the CM2010 and other devices.

The USB port is still a serial port which is /dev/cu.SLAB_USBtoUART on my Mac. Every second the device sends a package with 19200 baud 8N1. I’ve written a simple python script to demonstrate reading and interpreting the data. For actual use you should add some error handling.

Only one byte in the slot header is unknown (it seems the Windows software is also not using it) and the device header has a few semi-unknown ones (the version, the temperature, etc) – only the chemical setting is actually used by the Window software.

The full source code can be found on GitHub https://github.com/sarnau/cm2016.

ELV Mobile Alerts

Mobile Alerts

This document tries to describe every detail of the Mobile Alerts sensors, which are sold by ELV in Germany, but are also available at the common suspects (Amazon, etc). Be careful buying at Amazon: certain sensors mention Mobile Alerts, but seem to be designed for the US. They are not compatible with the ELV Mobile Alerts ones!

Mobile Alerts is covering mostly climate sensors, but also contains moisture and door/window sensors plus a sound detector, which acts as a gateway for smoke sensors.

The Mobile Alerts are a version of the LaCrosse Alerts Mobile system made for the European market.

Detailed Infomation

- Mobile Alerts ELV vs LaCrosse – Difference between ELV and LaCrosse sensors

- Mobile Alerts Devices – List of all devices with technical infos

- Mobile Alerts Sensor QR Code – QR Code format found on sensors

- Mobile Alerts Website – All data send into the cloud is available via a web-interface.

- Mobile Alerts Gateway – Serial number format, LED function

- Mobile Alerts Gateway Web Interface – Web interface of the Gateway

- Mobile Alerts Gateway UDP Protocol – Find/Configure a Gateway

- Mobile Alerts Gateway REST API – Public limited REST API

- Mobile Alerts Gateway Application API – API used by iOS application to read all data from the cloud

- Mobile Alerts Gateway Upload into Cloud – binary protocol used by the Gateway to upload sensor data into the Cloud

Mobile Alerts Sensors

ELV is selling affordable weather sensors http://www.elv.de/ip-wettersensoren-system.html, which can be monitored via an iOS application. To allow that all data is transmitted via a gateway to a server, which the application can access. Sadly the protocol is not documented. I don’t think anybody has documented the way the URL has been constructed, especially the MD5 hash over the first part of it.

This sample code integrates sensors into fhem and I wrote it for Mac OS X, but it should work on Linux, too.

All information (and more) is available on GitHub as well.

To integrate the sensors into fhem, add the sensors to the iOS application and check if they show up. You need to note all sensor IDs. The ID is 6 bytes long and represented as a hexadecimal number. This same code supports sensors of type 2 (temperature only) and type 3 (temperature and humidity), which can be recognized via the first two characters of the ID.

You have to adjust the following things in the code:

- sensors = … Here you have to add all sensors IDs as strings

- downloadPath This needs to be adjusted to point to the log folder of fhem.

- vendorid You might want to change the UUID to a new one (just run uuidgen from the terminal)

Python Code

#!/usr/bin/env python

# -*- coding: utf-8 -*-

import sys

import os

import json

import pprint

import datetime

import hashlib

import time

downloadPath = os.path.expanduser('~/fhem-5.7/log')

pp = pprint.PrettyPrinter()

sensors = set(['021122334455',...,'031122334455'])

def parseJSON(jj):

if not jj['success']:

print '#%d %s' % (jj['errorcode'],jj['errormessage'])

return

for device in jj['result']['devices']:

#pp.pprint(device)

deviceTypeId = device['devicetypeid']

deviceName = device['name']

print '%s %s [%d] #%d %s' % (device['deviceid'], deviceName, device['lowbattery'],len(device['measurements']),datetime.datetime.fromtimestamp(device['lastseen']).strftime('%Y-%m-%d %H:%M:%S'))

year = -1

month = -1

logPath = ''

for measurement in device['measurements']:

idx = measurement['idx']

transmitTime = datetime.datetime.fromtimestamp(measurement['c'])

measurementTime = datetime.datetime.fromtimestamp(measurement['ts'])

tx = measurement['tx']

mm = measurement

del mm['idx']

del mm['c']

del mm['ts']

del mm['tx']

if year != measurementTime.year or month != measurementTime.month:

if len(logPath):

f = open(logPath, "w")

for d in sorted(data):

f.write('%s %s\n' % (d,data[d]))

year = measurementTime.year

month = measurementTime.month

logPath = downloadPath + '/S_SENSOR_%s-%d-%02d.log' % (deviceName.upper().replace(' ','_'),year,month)

data = {}

try:

for line in open(logPath).readlines():

vals = line[:-1].split(' ')

data[' '.join(vals[:-1])] = vals[-1]

except:

pass

dataKey = measurementTime.strftime('%Y-%m-%d_%H:%M:%S') + ' SENSOR_' + deviceName.upper().replace(' ','_') + ' '

if deviceTypeId == 2:

data[dataKey + 'TEMP:'] = '%.1f' % (measurement['t1'])

elif deviceTypeId == 3:

data[dataKey + 'TEMP:'] = '%.1f' % (measurement['t1'])

data[dataKey + 'FEUCHTIGKEIT:'] = '%.1f' % (measurement['h'])

else:

pp.pprint(mm)

if len(logPath):

f = open(logPath, "w")

for d in sorted(data):

f.write('%s %s\n' % (d,data[d]))

import urllib

import urllib2

devicetoken = 'empty' # defaults to "empty"

vendorid = '1FB220C4-CC15-4195-97CF-8BE4FD3DAE72' # iOS vendor UUID (returned by iOS, any UUID will do). Launch uuidgen from the terminal to generate a fresh one.

phoneid = 'Unknown' # Phone ID - probably generated by the server based on the vendorid (this string can be "Unknown" and it still works)

version = '1.21' # Info.plist CFBundleShortVersionString

build = '248' # Info.plist CFBundleVersion

executable = 'Mobile Alerts' # Info.plist CFBundleExecutable

bundle = 'de.synertronixx.remotemonitor' # [[NSBundle mainBundle] bundleIdentifier]

lang = 'en' # preferred language

request = "devicetoken=%s&vendorid=%s&phoneid=%s&version=%s&build=%s&executable=%s&bundle=%s&lang=%s" % (devicetoken,vendorid,phoneid,version,build,executable,bundle,lang)

request += '&timezoneoffset=%d' % 60 # local offset to UTC time

request += '&timeampm=%s' % ('true') # 12h vs 24h clock

request += '&usecelsius=%s' % ('true') # Celcius vs Fahrenheit

request += '&usemm=%s' % ('true') # mm va in

request += '&speedunit=%d' % 0 # wind speed (0: m/s, 1: km/h, 2: mph, 3: kn)

request += '×tamp=%s' % datetime.datetime.utcnow().strftime("%s") # current UTC timestamp

requestMD5 = request + 'asdfaldfjadflxgeteeiorut0ß8vfdft34503580' # SALT for the MD5

requestMD5 = requestMD5.replace('-','')

requestMD5 = requestMD5.replace(',','')

requestMD5 = requestMD5.replace('.','')

requestMD5 = requestMD5.lower()

m = hashlib.md5()

m.update(requestMD5)

hexdig = m.hexdigest()

request += '&requesttoken=%s' % hexdig

request += '&deviceids=%s' % ','.join(sensors)

#request += '&measurementfroms=%s' % ('0,' * len(sensors))

#request += '&measurementcounts=%s' % ('50,' * len(sensors))

http_header = {

"User-Agent" : "remotemonitor/248 CFNetwork/758.2.8 Darwin/15.0.0",

"Accept-Language" : "en-us",

"Content-Type": "application/x-www-form-urlencoded; charset=utf-8",

"Host" : "www.data199.com:8080",

}

# create an urllib2 opener()

opener = urllib2.build_opener()

# create your HTTP request

req = urllib2.Request('http://www.data199.com:8080/api/v1/dashboard', request, http_header)

# submit your request

while True:

res = opener.open(req)

parseJSON(json.loads(res.read()))

print '-' * 40

time.sleep(10*60) # wait for 10 minutes

Atari ST Book: BIOS/XBIOS ROM listing

Atari ST ROM fully commented BIOS/XBIOS ROM listing for TOS 2.06, TOS 3.06 and – especially – the ST-Book ROM. I tried to collect the original comments from the Atari developers, when available. Also available on GitHub.

ROM_TOS206 EQU 1 ; regular TOS 2.06 ROM

ROM_TOS306 EQU 0 ; regular TOS 2.06 ROM

ROM_STBOOK EQU 0 ; ROM for the ST Book (variation of TOS 2.06)

osroml: bra.s reseth ; os_entry - BRA to reset handler

IF ROM_TOS306

DC.W $0306 ; os_version - TOS version number

ELSE

DC.W $0206 ; os_version - TOS version number

ENDIF

DC.L reseth ; os_reseth -> reset handler

DC.L osroml ; os_beg -> base of OS

DC.L endos ; os_end -> end BIOS/GEMDOS/VDI ram usage

DC.L reseth ; os_exec/os_rsv1 << unused, reserved >>

DC.L gem_mupb ; os_magic -> GEM memory usage param. block

IF ROM_STBOOK

DC.L $03101992 ; os_date - Date of system build ($YYYYMMDD)

ELIF ROM_TOS206

DC.L $11141991 ; os_date - Date of system build ($YYYYMMDD)

ELIF ROM_TOS306

DC.L $09241991 ; os_date - Date of system build ($YYYYMMDD)

ENDIF

DC.W $0000 ; os_conf - OS configuration bits

IF ROM_STBOOK

DC.W $186a ; os_dosdate - DOS-format date of system build

ELIF ROM_TOS206

DC.W $176e ; os_dosdate - DOS-format date of system build

ELIF ROM_TOS306

DC.W $1738 ; os_dosdate - DOS-format date of system build

ENDIF

DC.L ospool_base ; p_root -> base of OS pool

DC.L kb_shift ; pkbshift -> keyboard shift state variable

DC.L gemdos_pid ; p_run -> GEMDOS PID of current process

DC.L $000000 ; p_rsv2 << unused, reserved >>

*+

* [ROM based system]

* reseth - System reset handler

*

* Gains control of the system upon power-up reset,

* or when the RESET button is pressed,

* or after a really messy system crash.

*

*-

reseth: move #$2700,sr ; super mode, no interrupts

IF ROM_TOS306

move.w #$100,(fifo).w

move.w #0,(fifo).w

ENDIF

reset ; reset hardware

*+

* [ROM based system]

* Check for a diagnostic cartridge;

* if one is inserted, load a return address

* into A6 and jump into the cat's entry point.

*

*-

cmpi.l #$fa52235f,(cartbase).l ; is the magic number there?

bne.s reset1 ; (no)

lea reset1(pc),a6 ; a6 -> return address

jmp (cartbase+4).l ; execute diagnostic cartridge

*+

* [ROM based system]

* Is this is a warm reset, setup the memory

* controller configuration register so that

* the reset-bailout vector has something to

* stand on ....

*

*-

reset1:

IF ROM_TOS306

move.l #$808,d0

movec d0,cacr

moveq #0,d0 ; set vector base to address 0

movec d0,vbr

pmove ($e35fe4).l,tc ; 0L - disable PMMU

pmove ($e35fe4).l,tt0 ; 0L

pmove ($e35fe4).l,tt1 ; 0L

frestore ($e35fe4).l ; 0L - clear FPU

btst #0,(scu_gp1).w ; memconfig valid?

beq.s reset3 ; (no)

ENDIF

lea ret_1(pc),a6 ; load return addr

bra val_memval ; check memory configuration validity

ret_1: bne.s reset3 ; (invalid -- don't set anything up)

move.b (memcntlr).w,(memconf).w ; initialize memory controller

reset2:

IF ROM_STBOOK

move.w (STConfig).w,d0 ; Configuration on ST Book

cmp.b #$fc,d0 ; power pressed while the ST Book is closed?

beq.s reset2b ; yes => do not execute reset vector

move.w (tt_mcu+4).l,d0 ; ST Book: ???

and.b #6,d0 ; check bit 1 & 2

bne.s reset2c

reset2b: clr.l (resvalid).l

reset2c:

ENDIF

*+

* [ROM based system]

* RESET bailout vector check.

* Check to make sure we have a clean, well-bred

* bailout vector. The high byte must be zero,

* it must be even, and cannot be entirely zero.

*

*-

cmpi.l #$31415926,(resvalid).w ; is the resvalid the magic number?

bne.s reset3 ; (no)

move.l (resvector).w,d0 ; d0 = reset bailout vector

IF !ROM_TOS306

tst.b (resvector).w ; bits 24..31 must be zero

bne.s reset3 ; (they aren't, so punt)

ENDIF

btst #0,d0 ; the vector must be even

bne.s reset3 ; (it isn't, so punt)

movea.l d0,a0 ; a0 -> reset handler

lea reset2(pc),a6 ; a6 -> return address

jmp (a0) ; execute reset bailout

*+

* Initialize PSG output ports.

* Make port A and B output-only,

* initialize floppy select lines (so

* that none are selected)

*-

reset3: lea (psgsel).w,a0 ; a0 -> giselect, giwrite-2

move.b #7,(a0) ; set porta & portb to output

move.b #$c0,2(a0)

move.b #14,(a0) ; deselect disks

move.b #7,2(a0)

*+

* Determine 50hz or 60hz.

* The hardware RESETs to 60hz. Check a bit in the

* ROM configuration byte to see if we have to twiddle

* the hardware into 50hz mode.

*

*-

IF ROM_TOS306

move.b #1,(v_shf_mod).w ; Switch to 640x200x2

ELSE

btst #0,(osroml+29).l ; check bit: configured for 50hz?

beq.s notpal ; (nope -- we're good ol' NTSC)

lea ret_1b(pc),a6

bra waitvbl ; a short delay for PAL

ret_1b: move.b #2,(synmod).w ; yes -- twiddle to 50hz

notpal:

IF ROM_STBOOK

move.b #2,(v_shf_mod).w ; Switch to 640x400x1

move.b #$80,(lcdPowerControl).w ; LCD display on

tst.w (tt_mcu).l ; ST Book: ???

ENDIF

ENDIF

*+

* Initialize palette registers to

* their default values

*

*-

lea (palette).w,a1 ; a1 -> hardware reg

move.w #15,d0 ; setup 16 colors

lea colors(pc),a0 ; a0 -> table of default colors

sysic1: move.w (a0)+,(a1)+ ; copy palette assignment

dbra d0,sysic1 ; (loop for more colors)

*+

* On a ROM system, put the screen (temporarily)

* at $10000, so icon-drawing routines won't

* blow any any system variables.

*-

move.b #1,(v_bas_h).w ; set high ptr

clr.b (v_bas_m).w ; set low ptr

*+

* [ROM based system]

* Determine how much memory there is, and initialize

* the memory controller configuration register

*

*-

IF ROM_TOS306

btst #0,(scu_gp1).w ; memconfig valid?

beq.s checkmem ; (no)

ENDIF

move.b (memcntlr).w,d6 ; d6 = memory controller configuration

IF ROM_TOS306

move.b d6,(memconf).w ; setup memory controller configuration register

ENDIF

move.l (phystop).w,d5 ; d5 -> (possible) top of physical mem

lea ret_2(pc),a6 ; load return address

bra val_memval ; check if the memory configuration is valid

ret_2: beq reset4

IF ROM_STBOOK

*--- init vars + hardware:

move.b #%1010,d6 ; setup controller for 2Mb/2Mb - only valid configuration on a ST Book

move.b d6,(memconf).w ; setup memory controller

*--- write test-pattern to determine memory configuration:

move.l #$400000,d5 ; d5 -> physical top of memory (4Mb)

move.l #$6161964,d0 ; 16th June 1964...

move.l #$3251987,d1 ; 25th March 1987...

move.l d0,($300010).l

move.l d1,($300014).l

cmp.l ($300010).l,d0 ; test if 4MB is actually installed

bne.s ret_2a

cmp.l ($300014).l,d1

beq.s ret_2b

ret_2a: move.l #$100000,d5 ; d5 -> physical top of memory (1Mb)

ret_2b: lea ($8000).l,sp

ELIF ROM_TOS206

* First we try to configure the memory controller

clr.w d6

move.b #$a,(memconf).w ; default: setup controller for 2Mb/2Mb

movea.w #$8,a0

lea ($200008).l,a1 ; + 2Mb

clr.w d0

chkpatloop: move.w d0,(a0)+ ; fill 512-8 bytes with a test pattern

move.w d0,(a1)+

add.w #$fa54,d0

cmpa.w #$200,a0

bne.s chkpatloop

move.b #90,(v_bas_l).w ; wrote low byte of video address

tst.b (v_bas_m).w ; touch the middle byte (this should reset the low byte)

move.b (v_bas_l).w,d0

cmp.b #90,d0 ; low byte not reset?

bne.s chkmem1

clr.b (v_bas_l).w ; try a different low byte value

tst.w (palette).w ; touch the color palette

tst.b (v_bas_l).w ; low byte changed?

bne.s chkmem1

move.l #$40000,d7 ; 256Kb offset

bra.s chkmem1b

chkmem1: move.l #$200,d7 ; 512 byte offset

chkmem1b: move.l #$200000,d1 ; 2Mb = maximum size per bank

chkmemloop: lsr.w #2,d6 ; shift memory configuration down by a bank (bank 1 is in bits 0..1, bank 0 is in bits 2..3)

movea.l d7,a0 ; + 512/256Kb bytes

addq.l #8,a0

lea chkmem3(pc),a4

bra memchk

chkmem3: beq.s chkmem7 ; bank is not working =>

movea.l d7,a0

adda.l d7,a0 ; + 1024/512Kb byte

addq.l #8,a0

lea chkmem4(pc),a4

bra memchk

chkmem4: beq.s chkmem6 ; bank has 512Kb of memory =>

movea.w #$8,a0 ; + 0 bytes

lea chkmem5(pc),a4

bra memchk

chkmem5: bne.s chkmem7 ; bank is empty =>

addq.w #4,d6 ; 4+4 = 1000 2Mb bank size

chkmem6: addq.w #4,d6 ; 4 = 0100 512Kb bank size

chkmem7: sub.l #$200000,d1 ; - 2Mb

beq.s chkmemloop

move.b d6,(memconf).w ; set memory configuration

ELIF ROM_TOS306

checkmem:

move.w #5,d6

move.b #$a,(memconf).w

moveq #0,d0

move.l d0,($1008).w

move.l d0,($100c).w

move.l #$6161964,d0

move.l d0,($0008).w

cmp.l ($1008).w,d0

bne.s checkmem1

move.l #$4251987,d0

move.l d0,($000c).w

cmp.l ($100c).w,d0

beq.s checkmem2

checkmem1: move.w #$a,d6

checkmem2: move.b d6,(memconf).w

ENDIF

IF ROM_TOS206 || ROM_TOS306

* memory is configured, set the stack pointer

lea ($8000).l,sp

* test the memory in 128Mb blocks to find out the maximum installed

* physical memory. A failure (bus error or a memory checksum error)

* terminates the search.

movea.l (busexception).w,a4

lea chkmemx(pc),a0 ; if a bus error occurs, we are done, too

move.l a0,(busexception).w

move.w #$fb55,d3

move.l #$20000,d7 ; 128Mb is the page size for testing

movea.l d7,a0 ; 128Mb is the minimum physical memory

chkmem8: movea.l a0,a1 ; test just below the current top of memory

move.w d0,d2

moveq #$2a,d1 ; test 43 words

chkmem9: move.w d2,-(a1) ; write test pattern

add.w d3,d2

dbra d1,chkmem9

movea.l a0,a1

moveq #$2a,d1 ; check 43 words

chkmem10: cmp.w -(a1),d0 ; compare the test pattern

bne.s chkmemx ; test failed => we are done

clr.w (a1) ; erase memory after testing

add.w d3,d0

dbra d1,chkmem10

adda.l d7,a0 ; advance to the next page

bra.s chkmem8

chkmemx: suba.l d7,a0 ; the last page didn't work

move.l a0,d5 ; end of the physical memory

move.l a4,(busexception).w

ENDIF

*+

* [ROM based system]

* Clear memory from $400 to 'd5' (phystop)

*-

movea.w #etv_timer,a0 ; start at the beginning

move.l d5,d4 ; where to end

moveq #0,d0

clm_1: move.l d0,(a0)+ ; initialize all the memory

move.l d0,(a0)+

move.l d0,(a0)+

move.l d0,(a0)+

cmpa.l d4,a0 ; done?

bne.s clm_1 ; (loop for more bytes)

*+

* [ROM based system]

* Indicate that memory has successfully

* been sized and tested. Set two variables

* to magic values ...

*

*-

move.b d6,(memcntlr).w ; save configuration byte

move.l d5,(phystop).w ; save physical top-of-memory

move.l #$752019f3,(memvalid).w ; indicate memory was configured

move.l #$237698aa,(memval2).w ; ditto (paranoia variable)

move.l #$5555aaaa,(memval3).w ; ditto #2 (paranoia variable)

IF ROM_TOS306

move.l #fchkmemex,(busexception).w

move.w #0,(tt_mcu+224).l

fchkmemex:

* test the memory in 128Mb blocks to find out the maximum installed

* physical fast mem. A failure (bus error or a memory checksum error)

* terminates the search.

move.l #fchkmemx,(busexception).w ; if a bus error occurs, we are done, too

move.w #$fb55,d3

moveq #0,d0

move.l #$20000,d7 ; 128Mb is the page size for testing

movea.l #$1020000,a0 ; start address of fast mem area + 128Mb

fchkmem8: movea.l a0,a1 ; test just below the current top of memory

move.w d0,d2

moveq #$2a,d1 ; test 43 words

fchkmem9: move.w d2,-(a1) ; write test pattern

add.w d3,d2

dbra d1,fchkmem9

movea.l a0,a1

moveq #$2a,d1 ; check 43 words

fchkmem10: cmp.w -(a1),d0 ; compare the test pattern

bne.s fchkmemx ; test failed => we are done

clr.w (a1) ; erase memory after testing

add.w d3,d0

dbra d1,fchkmem10

adda.l d7,a0 ; advance to the next page

bra.s fchkmem8

fchkmemx: suba.l d7,a0 ; the last page didn't work

cmpa.l #$1000000,a0 ; it failed right at the beginning of the fast mem?

bne.s fchkmemno ; (no)

suba.l a0,a0 ; then we have no fast mem

fchkmemno: move.l a0,d5 ; end of the fast mem

move.l d5,(ramtop).w ; top of fast mem

move.l #$1357bd13,(ramvalid).w ; ramtop is valid (ramvalid == RAMMAGIC)

bset #0,(scu_gp1).w ; memconfig is valid

ELSE

clr.l (ramtop).l ; no FASTRAM available

move.l #$1357bd13,(ramvalid).w ; ramtop is valid (ramvalid == RAMMAGIC)

ENDIF

reset4: movea.l #_supstk+2048,sp ; setup supervisor stack

IF ROM_STBOOK

*+

* Initialize interrupt vectors

*

* The exception vectors are pointed to a cold boot (_coldboot)

* during startup.

*

* Trap 2 and Divide-by-zero are pointed at an rte

*

* The HBLANK, VBLANK, line 1001 [someday: line 1111), trap 13, trap 14,

* and "extended" trap vectors are initialized appropriately.

*

*-

lea _rte(pc),a3 ; a3 -> handy RTE

lea _rts(pc),a4 ; a4 -> handy RTS

*--- setup 64 vectors:

lea (_coldboot).l,a1 ; a1 -> during boot all exception trigger a coldboot, which erases all memory and resets

lea (busexception).w,a0 ; a0 -> interrupt RAM

move.w #$3f,d0 ; d0 = count

sei1: move.l a1,(a0)+ ; write vector

dbra d0,sei1 ; (loop to write more vectors)

move.l a3,(divzeroexception).w ; divide-by-zero vector -> rte

move.l a3,(Level7IRQ).w ; level #7 interrupt -> rte (power exception in a ST Book)

moveq #6,d0

lea (Level1IRQ_TTVME).w,a1

sei2: move.l #_rte,(a1)+ ; level #1 ... level #6 to RTE

dbra d0,sei2

*--- install OS interrupt vectors:

move.l #vbl,(Level4IRQ_VBL).w ; vblank handler

move.l #hbl,(Level2IRQ_HBL).w ; hblank handler

move.l a3,(trap_aesvdi).w ; (empty) trap#2 handler

move.l #trp13h,(trap_bios).w ; trap #13 handler

move.l #trp14h,(trap_xbios).w ; trap #14 handler

move.l #line1010,(lineAexception).w ;line 1010 handler

move.l a4,(etv_timer).w ; default timer-tick vector -> rts

move.l #_critich,(etv_critic).w ; default critical error handler

move.l a4,(etv_term).w ; default terminal vector -> rts

*+

* Setup the vblank deferred vector list.

* (This data structor is ugly,

* but we seem to be stuck with it).

*

*-

lea (_vbl_list).w,a0 ; a0 -> default list of vbl locs

move.l a0,(_vblqueue).w ; install ptr to them

move.w #7,d0 ; clear vbl vectors

avbl: clr.l (a0)+ ; one at a time

dbra d0,avbl

lea (tconstat).l,a0

movea.w #xconstat,a1

moveq #31,d0

tconl: move.l (a0)+,(a1)+

dbra d0,tconl

movea.l (busexception).w,a0

movea.l sp,a1

move.l #vmeinit,(busexception).w

move.b #$40,(vme_mask).w ; Enable IRQ6 from VMEBUS/MFP

move.b #$14,(sys_mask).w ; VSYNC & HSYNC enable in the VME Bus System Control Unit

vmeinit: move.l a0,(busexception).w

movea.l a1,sp

ENDIF

clr.b ($aa6).l

IF ROM_STBOOK

sf (STEFlag).l ; ST Book is not an Atari STE

ELSE

movea.l sp,a6

move.l #mwinitex,(busexception).w

clr.w (sndmactl).w

st ($a02).l ; microwire interface available

lea mwinitdata(pc),a0

move.w (a0)+,(mwmask).w

bra.s mwinit3

mwinitdata: DC.W $0ffe ; LMC 1992 mask

DC.W $09d1 ; 10-011-101000-1 = LCM - Master Volume - 0 db volume (max) - end-bit

DC.W $0aa9 ; 10-101-010100-1 = LCM - Left channel volume - 0 db volume (max) - end-bit

DC.W $0a29 ; 10-100-010100-1 = LCM - Right channel volume - 0 db volume (max) - end-bit

DC.W $090d ; 10-010-000110-1 = LCM - Trebble control - 0 db (linear) - end-bit

DC.W $088d ; 10-001-000110-1 = LCM - Bass control - 0 db (linear) - end-bit

DC.W $0803 ; 10-000-000001-1 = LCM - Mixer - DMA + YM2149 - end-bit

DC.W $0000 ; 0 = end of list

mwinit1: move.w d0,(mwdata).w

mwinit2: tst.w (mwdata).w

bne.s mwinit2

mwinit3: move.w (a0)+,d0

bne.s mwinit1

mwinitex: movea.l a6,sp

IF ROM_TOS206

move.b #90,(v_bas_l).w ; write low byte of video address

tst.b (v_bas_m).w ; access the medium byte

move.b (v_bas_l).w,d0 ; (which should reset the low byte on an STE!)

cmp.b #90,d0 ; reset?

bne.s nostedetect ; yes => STE detected

clr.b (v_bas_l).w ; clear the low byte again

tst.w (palette).w ; access the color palette

tst.b (v_bas_l).w

nostedetect:sne (STEFlag).l ; <>0 => no STE hardware available

ELSE

sf (STEFlag).l ; no STE hardware available

ENDIF

ENDIF

*+

* Clear OS bss (from 'endosbss' to 'ostext')

*-

movea.l #ostext,a1 ; a1 -> end

movea.l #endosbss,a0 ; a0 -> start

*--- common code to clear memory:

moveq #0,d0 ; quick zero

clrm_1: move.w d0,(a0)+ ; clobber a word

cmpa.l a0,a1 ; at end?

bne.s clrm_1 ; (no -- loop for more words)

IF ROM_TOS306

bsr setupPMMU ; setup PMMU translation table

ENDIF

*+

* Setup display base,

* clear display memory.

*

*-

movea.l (phystop).w,a0 ; video_base = phystop - 0x8000

IF !ROM_TOS306

suba.l #$8000,a0 ; screen size = 32kb

move.w #$7ff,d1 ; d1 = # 16-byte chunks to zero

ELSE

suba.l #$25900,a0 ; screen size = 154kb

move.w #$258f,d1 ; d1 = # 16-byte chunks to zero

ENDIF

move.l a0,(_v_bas_adr).w

move.b (_v_bas_adr+1).w,(v_bas_h).w ;load high addr

move.b (_v_bas_adr+2).w,(v_bas_m).w ;load low (really, medium) addr

moveq #0,d0 ; quick zero

clrm_2: move.l d0,(a0)+ ; zero a longword

move.l d0,(a0)+ ; zero a longword

move.l d0,(a0)+ ; zero a longword

move.l d0,(a0)+ ; zero a longword

dbra d1,clrm_2 ; (loop for more longwords)

*+

* Initialize all kinds of OS variables

*

*-

*--- OS parameters:

movea.l osroml+20(pc),a0 ; get pointer to magic

cmpi.l #$87654321,(a0) ; is the magic there?

beq.s usem

lea (osroml+8).l,a0 ; yes -- use numbers there

usem: move.l 4(a0),(end_os).w ; init end-of-OS pointer

move.l 8(a0),(exec_os).w ; init default-shell pointer

*--- Disk vectors:

move.l #_dskinit,(hdv_init).w ; initialization

move.l #_floprw,(hdv_rw).w ; read/write absolute sectors

move.l #_getbpb,(hdv_bpb).w ; media change inquiry

move.l #_mediach,(hdv_mediach).w ; get BIOS parameter block

move.l #_boot,(hdv_boot).w ; boot-from-device

move.l #_lstostat,(prv_lsto).w

move.l #_lstout,(prv_lst).w

move.l #_auxostat,(prv_auxo).w

move.l #_auxout,(prv_aux).w

move.l #_scrdmp,(scr_dump).w

*--- Randoms:

move.l (_v_bas_adr).w,(_memtop).w ;_memtop = _v_bas_ad

move.l (end_os).w,(_membot).w ; set bottom of memory (for DOS)

move.w #8,(nvbls).w ; default number of vbl queue entries

st (_fverify).w ; enable write-verify

move.w #3,(seekrate).w ; set default seek-rate

move.l #_diskbuf,(_dskbufp).w ; set pointer to disk buffer

move.w #-1,(_prtcnt).w ; initialize print-count

move.l #osroml,(_sysbase).w ; -> base of OS

move.l #savend,(savptr).w ; register-save pointer for traps 13&14

move.l #_rts,(swv_vec).w ; ignore monitor changes for now

clr.l (_drvbits).w ; remove all drives

move.l #keybellsnd,(bell_hook).w

move.l #keyclicksnd,(kcl_hook).w

bsr sysbase2ram ; copy sysbase into RAM and patch os_conf to contain os_dosdate

*--- Cookies:

lea (cookieBuffer).l,a0

move.l a0,(_p_cookies).w

move.l #'_CPU',(a0)+

moveq #0,d1 ; 68000 CPU

movea.w #illegalexception,a2

movea.l (a2),a3

movea.l sp,a1

move.l #cookieCPU,(a2)

move ccr,d0 ; first exists in the 68010

moveq #10,d1 ; 68010 CPU

extb.l d0 ; first exists in the 68020

moveq #20,d1 ; 68020 CPU

movec cacr,d0

bset #9,d0

movec d0,cacr

movec cacr,d0

bclr #9,d0

beq.s cookieCPU

moveq #30,d1 ; 68030 CPU

movec d0,cacr

cookieCPU: movea.l a1,sp

move.l a3,(a2)

move.l d1,(a0)+

sne (_longframe+1).w ; 68010+ have a longer interrupt stack frame

IF ROM_STBOOK

move.l #'_VDO',(a0)+ ; setup VDO cookie: Video hardware

move.l #$10001,(a0)+ ; 1,1 => Atari STE, ST-Book

move.l #'_MCH',(a0)+ ; setup MCH cookie: Machine type

move.l #$10001,(a0)+ ; 1,1 => Atari STE, ST-Book

move.b #$7f,d0

tst.b (STEFlag).l

bne.s cookieSTE

move.l #'_SWI',(a0)+ ; setup SWI cookie: DIP configuration switches

moveq #0,d0

move.w (STConfig).w,d0

lsr.w #8,d0

move.l d0,(a0)+ ; all DIP switches as a bit mask 0..7

cookieSTE: moveq #3,d1 ; bit 0: PSG, bit 1: 8-bit DMA

move.l #'_SND',(a0)+ ; setup SND cookie: Sound hardware

btst #7,d0 ; DIP switch 7 on?

bne.s cookieSND ; (punt)

bclr #1,d1 ; no 8-bit DMA sound

cookieSND: move.l d1,(a0)+

btst #6,d0 ; DIP switch 6 on?

bne.s cookieFDC ; (punt - no HD floppy)

move.b #8,(dsb0).l ; select HD density for drive A

move.l #'_FDC',(a0)+ ; setup FDC cookie: Floppy disk controller

move.l #$1415443,(a0)+ ; 'FDC' | (1 << 24)

cookieFDC: move.l #'_FPU',(a0)+ ; Setup FPU cookie: Type of the FPU

moveq #0,d7 ; 0 = no FPU

suba.w #$24,sp

move.l (lineFexception).w,(sp)

move.l (coprocexception).w,4(sp)

move.l #cookieFPU,(lineFexception).w

move.l #cookieFPU,(coprocexception).w

lea 8(sp),a1

movea.w #ffcp_unorderedcond,a2

move.l #cookieFPU2,d0

move.l (a2),(a1)+

move.l d0,(a2)+

move.l (a2),(a1)+

move.l d0,(a2)+

move.l (a2),(a1)+

move.l d0,(a2)+

move.l (a2),(a1)+

move.l d0,(a2)+

move.l (a2),(a1)+

move.l d0,(a2)+

move.l (a2),(a1)+

move.l d0,(a2)+

move.l (a2),(a1)+

move.l d0,(a2)+

clr.l -(sp)

movea.l sp,a2

frestore (sp)

cookieFPU2: move.l #$20000,d7 ; 0x20000 = 68881 or 68882 as co-processor (Exact type unknown)

cookieFPU: movea.l a2,sp

addq.w #4,sp

move.l (sp)+,(lineFexception).w

move.l (sp)+,(coprocexception).w

move.l (sp)+,(ffcp_unorderedcond).w

move.l (sp)+,(ffcp_inexactresult).w

move.l (sp)+,(ffcp_divzero).w

move.l (sp)+,(ffcp_underflow).w

move.l (sp)+,(ffcp_operanderror).w

move.l (sp)+,(ffcp_inexactresult).w

move.l (sp)+,(ffcp_divzero).w

move.l d7,(a0)+

movea.l (busexception).w,a1

movea.l sp,a2

move.l #cookieFPU3,(busexception).w

move.w (FPStat).w,d0

bset #0,-3(a0) ; SFP004 present

cookieFPU3: move.l a1,(busexception).w

movea.l a2,sp

ELSE

IF ROM_TOS206

tst.b (STEFlag).l ; no STE hardware available?

beq.s cookieMCH ; (correct)

move.l #'_VDO',(a0)+

clr.l (a0)+ ; 0,0 = Atari ST (260 ST, 520 ST, 1040 ST, Mega ST, ...)

move.l #'_MCH',(a0)+

clr.l (a0)+ ; 0,0 = Atari ST

bra.s cookieSWI

cookieVDO: move.l #'_VDO',(a0)+

move.l #$10000,(a0)+ ; 1,0 = STE Shifter

move.l #$10000,d0 ; x = $00 = regular STE

movea.l (busexception).w,a1

movea.l sp,a2

move.l #cookieMCH1,(busexception).w

tst.b (scu_gp1).w

move.w #$10,d0 ; x = $10 = Mega STE (with SCSI)

bra.s cookieMCH2

cookieMCH1: clr.w d0

movea.l a2,sp

move.l #cookieMCH2,(busexception).w

tst.b (ide_stat2).l

move.w #8,d0 ; x = $08 = STE with IDE (unknown machine)

cookieMCH2: move.l a1,(busexception).w

movea.l a2,sp

move.l #'_MCH',(a0)+

move.l d0,(a0)+ ; 1,x = STE (520, 1040, 2080, 4160, Mega STE, ST Book)

ELIF ROM_TOS306

move.l #'_VDO',(a0)+

move.l #$20000,(a0)+ ; 2,0 = TT Shifter

move.l #'_MCH',(a0)+

move.l #$20000,(a0)+ ; 2,0 = TT

ENDIF

cookieSWI: move.b #$7f,d0

tst.b (STEFlag).l ; no STE hardware available?

bne.s cookieSND2 ; (correct)

move.l #'_SWI',(a0)+ ; setup SWI cookie: DIP configuration switches

moveq #0,d0

move.w (STConfig).w,d0

lsr.w #8,d0

move.l d0,(a0)+

cookieSND2: moveq #3,d1 ; bit 0: PSG, bit 1: 8-bit DMA

move.l #'_SND',(a0)+ ; setup SND cookie: Sound hardware

btst #7,d0 ; DIP switch 7 on?

bne.s cookieSND3 ; (punt)

bclr #1,d1 ; no 8-bit DMA sound

cookieSND3: move.l d1,(a0)+

btst #6,d0 ; DIP switch 6 on?

bne.s cookieFDC2 ; (punt - no HD floppy)

move.b #8,(dsb0).l ; select HD density for drive A

move.l #'_FDC',(a0)+ ; setup FDC cookie: Floppy disk controller

move.l #$1415443,(a0)+ ; 'FDC' | (1 << 24)

cookieFDC2:

move.l #'_FPU',(a0)+ ; Setup FPU cookie: Type of the FPU

movea.l (lineFexception).w,a1

movea.l (coprocexception).w,a2

movea.l sp,a3

move.l #cookieFPUex,(lineFexception).w

move.l #cookieFPUex,(coprocexception).w

fmove.l d0,fp0

move.l #$20000,(a0)+ ; 6888x present

bra.s cookieFPUe2

cookieFPUex:clr.l (a0)+

cookieFPUe2:move.l a1,(lineFexception).w

move.l a2,(coprocexception).w

movea.l a3,sp

movea.l (busexception).w,a1

movea.l sp,a2

move.l #cookieFPUe3,(busexception).w

move.w (FPStat).w,d0

bset #0,-3(a0) ; SFP004 present

cookieFPUe3:move.l a1,(busexception).w

movea.l a2,sp

IF ROM_TOS306

tst.l (ramtop).w ; fast mem installed?

beq.s nfrbcookie ; (no)

move.l #'_FRB',(a0)+ ; allocate FRB cookie for DMA buffer

move.l (_membot).w,d0

move.l d0,(a0)+ ; buffer adress

add.l #$10000,d0 ; 64kb size

move.l d0,(_membot).w ; adjust memory base

move.l d0,(end_os).w

nfrbcookie:

ENDIF

ENDIF

clr.l (a0)+ ; terminate cookie list

move.l #$10,(a0)+ ; 16 available slots in the cookie store

IF !ROM_STBOOK

*+

* Initialize interrupt vectors

*

* The exception vectors are pointed to a cold boot (_coldboot)

* during startup.

*

* Trap 2 and Divide-by-zero are pointed at an rte

*

* The HBLANK, VBLANK, line 1001 [someday: line 1111), trap 13, trap 14,

* and "extended" trap vectors are initialized appropriately.

*

*-

lea _rte(pc),a3 ; a3 -> handy RTE

lea _rts(pc),a4 ; a4 -> handy RTS

*--- setup 62 vectors:

lea _term(pc),a1 ; _term -> draw number of bombs

IF !ROM_TOS306

adda.l #$2000000,a1 ; exception number in top 8 bits of the address

ENDIF

lea (busexception).w,a0 ; a0 -> interrupt RAM

move.w #$3d,d0 ; d0 = count

sei1: move.l a1,(a0)+ ; write vector

IF !ROM_TOS306

adda.l #$1000000,a1 ; increment the exception number

ENDIF

dbra d0,sei1 ; (loop to write more vectors)

move.l a3,(divzeroexception).w ; divide-by-zero vector -> rte

move.l a3,(Level7IRQ).w ; level #7 interrupt -> rte (power exception in a ST Book)

moveq #6,d0

lea (Level1IRQ_TTVME).w,a1

sei2: move.l #_rte,(a1)+ ; level #1 ... level #6 to RTE

dbra d0,sei2

*--- install OS interrupt vectors:

move.l #vbl,(Level4IRQ_VBL).w ; vblank handler

move.l #hbl,(Level2IRQ_HBL).w ; hblank handler

move.l a3,(trap_aesvdi).w ; (empty) trap#2 handler

move.l #trp13h,(trap_bios).w ; trap #13 handler

move.l #trp14h,(trap_xbios).w ; trap #14 handler

move.l #line1010,(lineAexception).w ;line 1010 handler

move.l a4,(etv_timer).w ; default timer-tick vector -> rts

move.l #_critich,(etv_critic).w ; default critical error handler

move.l a4,(etv_term).w ; default terminal vector -> rts

*+

* Setup the vblank deferred vector list.

* (This data structor is ugly,

* but we seem to be stuck with it).

*

*-

lea (_vbl_list).w,a0 ; a0 -> default list of vbl locs

move.l a0,(_vblqueue).w ; install ptr to them

move.w #7,d0 ; clear vbl vectors

avbl: clr.l (a0)+ ; one at a time

dbra d0,avbl

lea (tconstat).l,a0

movea.w #xconstat,a1

moveq #31,d0

tconl: move.l (a0)+,(a1)+

dbra d0,tconl

movea.l (busexception).w,a0

movea.l sp,a1

move.l #vmeinit,(busexception).w

move.b #$40,(vme_mask).w ; Enable IRQ6 from VMEBUS/MFP

move.b #$14,(sys_mask).w ; VSYNC & HSYNC enable in the VME Bus System Control Unit

vmeinit: move.l a0,(busexception).w

movea.l a1,sp

ENDIF

*+

* "The other half" of the BIOS handles character I/O,

* call its initialization hoook.

* (It can "never fail". This will get interesting

* if we ever to a detachable keyboard ....)

*-

bsr initmfp

move.w #$400,d0 ; Delay Mode, /50 Prescale, data = 0 (about 10us delay)

bsr mfpdelay

move.l #setikbd,-(sp)

move.w #1,-(sp)

jsr (ikbdws).l ; reset ikbd

addq.l #6,sp

move.w #$700,d0 ; Delay Mode, /200 Prescale, data = 0 (about 40us delay)

move.w #14,d1 ; 15 * 40us = 600us delay

ikbddelay: bsr mfpdelay

dbra d1,ikbddelay

*+

* Fire up %%2 cartridges

*

*-

moveq #2,d0 ; bit# = 2

bsr cartscan ; execute cartridge aps

IF ROM_STBOOK

bsr cartscan_STBOOK_EXTROM

move.b #$80,(lcdPowerControl).w ; LCD display on

move.b #$80,(lcdPowerControlShadow).w ; LCD display shadow register

moveq #2,d1 ; Switch to 640x400x1

lea setvb1(pc),a6

bra waitvbl

setvb1: move.b d1,(v_shf_mod).w ; set rez hardware register

ELIF ROM_TOS206

moveq #0,d1 ; Switch to 320x200x4

btst #7,($fffffa01).w ; monochrome monitor connected?

bne.s nomonomon ; (no)

moveq #2,d1 ; Switch to 640x400x1

nomonomon:

lea setvb1(pc),a6

bra waitvbl

setvb1: move.b d1,(v_shf_mod).w ; set rez hardware register

ELIF ROM_TOS306

moveq #4,d1 ; Switch to 640x480x4

btst #7,($fffffa01).w ; monochrome monitor connected?

bne.s nomonomon ; (no)

moveq #6,d1 ; Switch to 1280x960x1

nomonomon:

move.b d1,(shift_tt).w

ENDIF

move.b d1,(sshiftmd).w ; set rez shadow

bsr blittest

jsr ($e072aa).l ; linaA blitter/no-blitter table init

jsr (esc_init).l ; clear screen, initialize cursor

move.l #reseth,(swv_vec).w ; RESET system on monitor change

move.w #1,(vblsem).w ; enable vblank processing

*+

* [1] Fire up %%0 cartridges

* [2] Enable interrupts

* [3] Fire up %%1 cartridges

*

*-

clr.w d0 ; magic bit# = 0

bsr cartscan ; execute cartridge aps

IF ROM_STBOOK

bsr cartscan_STBOOK_EXTROM

ENDIF

move #$2300,sr ; Enable interrupts, go to IPL 3

moveq #1,d0 ; magic bit# = 1

bsr cartscan ; execute cartridge aps

IF ROM_STBOOK

bsr cartscan_STBOOK_EXTROM

move.l (_hz_200).w,d0

addq.l #3,d0

resDelayL: cmp.l (_hz_200).w,d0 ; a short delay of 15-20ms

bhi.s resDelayL

clr.b (kb_shift).l ; reset keyboard shift state

ENDIF

move.l #privinstr_exception,(privexception).w ;Emulate the MOVE SR so it works in usermode on a 68020+

bra resetcont

*+

* Flush instruction and data cache (68020+)

*-

flushCaches:move sr,-(sp)

ori #$700,sr

movec cacr,d0

or.l #$808,d0 ; CI (Clear Instruction Cache), DI (Clear Data Cache)

movec d0,cacr

move (sp)+,sr

rts

*+

* Emulate the MOVE SR,<ea> so it works in usermode on 68010+

*-

privinstr_exception:movem.l d0-d2,-(sp)

move.l a1,-(sp)

move.l a0,-(sp)

movea.l $16(sp),a0 ; a0 -> pc

move.w (a0),d0 ; d0 -> current opcode

move.w d0,d1 ; d1 -> save current opcode

and.w #$ffc0,d0

cmp.w #$40c0,d0 ; move SR,<ea>?

bne privinstr_exception_term ; (no -- punt)

move.l #$30004e71,(endosbss).w ; move.w d0,d0, nop

move.l #'NqNu',(endosbss+2*2).w ; nop, rts

move.w d1,d0

and.w #7,d0 ; <ea> register (bit 0..2)

lsl.w #8,d0

lsl.w #1,d0 ; move into bit 9..11 of the destination <ea>

or.w d0,(endosbss).w

move.w d1,d0

and.w #$38,d0 ; <ea> mode (bit 3..5)

lsl.w #3,d0 ; move into bit 6..8 of the destination <ea>

or.w d0,(endosbss).w ; generate a MOVE D0,<ea> from the MOVE SR,<ea> opcode

moveq #2,d2 ; opcode size = 2

cmp.w #$180,d0 ; <ea> == d8(An,Xn)?

beq privinstr_exception_term ; not supported -> _term

tst.w d0 ; <ea> == Dn?

beq.s privinstr_exception_dn

cmp.w #$140,d0 ; <ea> == d16(An)?

beq.s privinstr_exception_d16

cmp.w #$1c0,d0 ; <ea> == (xxx).w or (xxx).l?

bne.s privinstr_exception_other

* <ea> = (xxx).l or (xxx).w

and.w #7,d1 ; register == 0 => (xxx).w

beq.s privinstr_exception_abs16

addq.w #2,d2 ; it is (xxx).l -> opcode size += 2

move.w 4(a0),(endosbss+2*2).w ; move lower word of the absolute address

privinstr_exception_abs16:addq.w #2,d2 ; opcode size += 2

move.w 2(a0),(endosbss+2).w ; move upper word of the absolute address

bra.s privinstr_exception_ea ; -> regular destination ea

* <ea> = d16(An)

privinstr_exception_d16:addq.w #2,d2 ; opcode size += 2

move.w 2(a0),(endosbss+2).w ; move d16 offset

privinstr_exception_other:and.w #7,d1 ; d1 = An from the destination <ea>

cmp.w #7,d1 ; relative to A7?

bne.s privinstr_exception_ea ; no -> regular destination ea

* <ea> = d16(A7) or d8(A7,Dn)

* Special case because A7 has to be the USP, instead of the current SSP (in A7)

move usp,a1 ; have to use the USP, otherwise we wouldn't have gotten the exception

andi.w #$f3ff,(endosbss).w ; convert A7-relative into A1-relative destination <ea>

add.l d2,$16(sp) ; pc += opcode size

IF ROM_TOS306

bsr flushCaches

ENDIF

move.w $14(sp),d0 ; d0 = SR

jsr (endosbss).w ; execute: MOVE D0,d(A1,Dn); NOP; RTS or MOVE D0,d(A1); NOP; RTS

move a1,usp ; restore USP, but shouldn't have changed anyway

movea.l (sp)+,a0 ; restore registers

movea.l (sp)+,a1

movem.l (sp)+,d0-d2

rte ; continue execution

* <ea> = Dn

privinstr_exception_dn:add.l d2,$16(sp) ; pc += opcode size

ori.w #$10,(endosbss).w ; source ea = (A0)

IF ROM_TOS306

bsr flushCaches

ENDIF

lea 20(sp),a0 ; point to SR register to SSP

movem.l 8(sp),d0-d2 ; restore d0-d2

jsr (endosbss).w ; execute: MOVE (A0),Dn; NOP; NOP; RTS

movea.l (sp)+,a0 ; restore registers

movea.l (sp)+,a1

adda.w #$c,sp ; skip d0-d2, because they have already been restored

rte ; continue execution

privinstr_exception_ea:add.l d2,$16(sp) ; pc += opcode size

IF ROM_TOS306

bsr flushCaches

ENDIF

movea.l (sp)+,a0

movea.l (sp)+,a1

move.w 12(sp),d0 ; d0 = SR

jsr (endosbss).w ; execute: MOVE D0,<ea>; ...; RTS

movem.l (sp)+,d0-d2 ; restore registers

rte ; continue execution

privinstr_exception_term:movea.l (sp)+,a0 ; restore registers

movea.l (sp)+,a1

movem.l (sp)+,d0-d2

jmp (_term).l ; illegal instruction => _term

*+

* Load shell (if _cmdload is nonzero)

* or execute GEM in ROM

*-

resetcont: jsr (osi).l ; initialize DOS

*--- set the current system time and date

move.w (osroml+30).l,(systemDate).l ;use BIOS time as current time

jsr (readCurrentTime).l ; set current time to RTC time

beq.s notimechip ; (no RTC)

bsr readIKBDTime ; read time from the keyboard controller

swap d0

tst.b d0

beq.s notimechip ; (not valid either)

move.w d0,(systemDate).l ; update system time

swap d0

move.w d0,(systemTime).l

notimechip: clr.b (tacr).w

bclr #5,(iera).w ; disable Timer A interrupts

IF ROM_TOS306

move.l #$3111,d0

movec d0,cacr

ENDIF

movea.l #atari_image,a0 ; draw Atari Logo on the screen

movea.l (_v_bas_adr).w,a1

move.b (sshiftmd).w,d0

cmp.b #2,d0 ; 640 x 400 (bw)

beq.s drawLogobw ; (yes)

cmp.b #6,d0 ; 1280 x 960 (bw)

beq.s drawLogobw ; (yes)

IF ROM_TOS306

adda.w #4*320,a1

ELSE

adda.w #4*160,a1

ENDIF

move.w #86-1,d0 ; 86 lines

drawLogoc1: moveq #6-1,d1 ; 6 words per raster line

drawLogoc2: move.w (a0)+,d2 ; draw 4 plane Atari Logo

move.w d2,(a1)+

move.w d2,(a1)+

move.w d2,(a1)+

move.w d2,(a1)+

dbra d1,drawLogoc2

IF ROM_TOS306

adda.w #320-6*8,a1

ELSE

adda.w #160-6*8,a1

ENDIF

dbra d0,drawLogoc1

bra.s drawLogo3b

drawLogobw:

IF ROM_TOS306

adda.w #4*160,a1

ELSE

adda.w #4*80,a1

ENDIF

move.w #86-1,d0 ; 86 lines

drawLogobw2:moveq #12-1,d1 ; 12 bytes per raster line

drawLogobw3:move.b (a0)+,(a1)+ ; draw 1 plane Atari Logo

dbra d1,drawLogobw3

IF ROM_TOS306

adda.w #160-12,a1

ELSE

adda.w #80-12,a1

ENDIF

dbra d0,drawLogobw2

drawLogo3b: moveq #32+7,d7 ; y = 7

tst.b (sshiftmd).w

bne.s drawLogo4

moveq #32+12,d7 ; y = 12

drawLogo4: move.l #$30002,d6

move.w #$1b,-(sp)

move.l d6,-(sp)

trap #$d ; Bconout(2, ESC)

move.w #$59,4(sp)

move.l d6,(sp)

trap #$d ; Bconout(2, 'Y')

move.w d7,4(sp)

move.l d6,(sp)

trap #$d ; Bconout(2, ' '+0)

move.w #$20,4(sp)

move.l d6,(sp)

trap #$d ; Bconout(2, ' '+y)

addq.w #6,sp

IF !ROM_TOS306

cmpi.l #$3e80,(_hz_200).l ; system running for >80s?

bcc ptch_term ; (then no ROM CRC check)

ENDIF

*--- Check the ROM CRC

checkROM:

IF ROM_STBOOK

move.l #$3fffe,d7 ; offset to ROM CRC (last 2 bytes)

move.w #0,d6 ; number of banks = 1

ELIF ROM_TOS206

move.l #$1fffe,d7 ; offset to ROM CRC (last 2 bytes)

move.w #1,d6 ; number of banks = 2

ELIF ROM_TOS306

move.l #$1fffe,d7 ; offset to ROM CRC (last 2 bytes)

move.w #3,d6 ; number of banks = 4

ENDIF

movea.l #osroml,a5 ; ROM base address

checkROMl:

IF ROM_STBOOK

move.w #1,-(sp) ; checksum over every byte

ELIF ROM_TOS206

move.w #2,-(sp) ; checksum over every other byte

ELIF ROM_TOS306

move.w #4,-(sp) ; checksum over every 4th byte

ENDIF

move.l d7,-(sp) ; number of bytes

move.l a5,-(sp) ; buffer address

bsr calccrc

adda.w #10,sp

movea.l a5,a0

IF ROM_STBOOK

adda.l d7,a0

ELIF ROM_TOS206

adda.l #$3fffc,a0

ELIF ROM_TOS306

adda.l #$7fff8,a0

ENDIF

move.b (a0),d1 ; high byte of CRC

lsl.w #8,d1

IF ROM_STBOOK

move.b 1(a0),d1 ; low byte of CRC

ELIF ROM_TOS206

move.b 2(a0),d1 ; low byte of CRC

ELIF ROM_TOS306

move.b 4(a0),d1 ; low byte of CRC

ENDIF

cmp.w d1,d0 ; CRC identical?

bne.s checkROMbad ; (no)

addq.l #1,a5 ; next bank

dbra d6,checkROMl

bra.s ptch_term

badCRCtext: DC.B 'WARNING: BAD ROM CRC IN CHIP ',0

badCRCtextB:DC.B '.\r\n',0

checkROMbad:move.l a5,d5

pea (badCRCtext).l

move.w #9,-(sp)

trap #1

move.b #'E',d0 ; 'E' - even

btst #0,d5

beq.s checkROMbad2

move.b #'O',d0 ; 'O' - odd

checkROMbad2:move.w d0,2(sp)

move.w #2,(sp)

trap #1

IF ROM_TOS306

move.b #'E',d0 ; 'E' - even

btst #1,d5

beq.s checkROMbad3

move.b #'O',d0 ; 'O' - odd

checkROMbad3:move.w d0,2(sp)

move.w #2,(sp)

trap #1

ENDIF

move.l #badCRCtextB,2(sp)

move.w #9,(sp)

trap #1

addq.w #6,sp

addq.l #1,a5

dbra d6,checkROMl

* if no monochrome is active, holding down the alternate key forces

* to 320x200x4 instead of 640x480x4 for ST compatibility

IF ROM_TOS306

cmpi.b #6,(sshiftmd).w ; TT high?

beq.s ttlowreschk ; (yes)

move.l #$bffff,-(sp)

trap #$d ; Kbshift()

addq.w #4,sp

btst #3,d0 ; alternate pressed?

beq.s ttlowreschk ; (no)

clr.w -(sp)

pea ($ffffffff).w

pea ($ffffffff).w

move.w #5,-(sp)

trap #$e ; switch to low-res

adda.w #$c,sp

move.l #$808,d0

movec d0,cacr

ttlowreschk:

ENDIF

* During boot till this point any exception triggers a _coldboot, which

* erases the first MB and resets. From now own we point the exceptions

* to _term, which draws the bombs and terminates the currently running app

ptch_term:

IF ROM_STBOOK

move.l #$1000000,d1 ; d1 -> exception number

lea _term(pc),a0 ; new exception vector

adda.l d1,a0 ; add the exception number into the upper 8 bits (2 = bus error)

adda.l d1,a0

lea (busexception).w,a1 ; start with the bus error exception

move.w #$3f,d0

move.l #_coldboot,d2 ; old exception vector

ptch_term1: cmp.l (a1)+,d2 ; is it pointing to _coldboot?

bne.s ptch_term2 ; no -> ignore It

move.l a0,$fffc(a1) ; point it to _term

ptch_term2: adda.l d1,a0 ; increment the exception number in the upper 8 bits

dbra d0,ptch_term1 ; next vector ->

ENDIF

bsr _dskboot ; attempt to boot from disk

bsr mtest ; memory test and attempt to boot from DMA

bsr runresapps ; execute resident applications in memory

tst.w (_cmdload).l ; load shell from disk?

beq.s st_1 ; (no -- execute GEM in ROM)

bsr _auto

move.l #osroml,(_sysbase).l ; -> base of OS

pea nullenv(pc) ; null environment string

pea nullenv(pc) ; null argument string

pea cmdname(pc) ; push shell filename

clr.w -(sp) ; load-and-go flavor of execute

bra.s st_x ; exec shell ("never return")

*--- bring up GEM:

st_1: bsr _auto ; do auto-exec

IF ROM_STBOOK

bsr _auto_ROMDISK

ENDIF

move.l #osroml,(_sysbase).l ; -> base of OS

*--- kludge up an enviroment string

lea orig_env(pc),a0 ; kludge up an environment string, a0 -> original environment string

movea.l #the_env,a1 ; a1 -> place to put it

st_2: cmpi.b #'#',(a0) ; look for drive# character

bne.s st_3 ; (not it)

movea.l a1,a2 ; a2 -> place to put drive#

st_3: move.b (a0)+,(a1)+ ; copy a byte

bpl.s st_2 ; copy while not end-of-string

move.b (_bootdev).l,d0 ; compute drive#, and shove it

add.b #$41,d0 ; into the env string at the

move.b d0,(a2) ; appropriate spot

*--- kludge up an enviroment string:

pea (the_env).l ; push address of environment string

pea (nullenv).l ; no arguments

pea nullenv(pc) ; null shell name (in ROM, after all)

move.w #5,-(sp) ; createPSP flavor of exec

move.w #$4b,-(sp) ; exec function#

trap #1 ; get pointer to PSP

adda.w #14,sp ; (clean up cruft)

movea.l d0,a0 ; a0 -> PSP

move.l (exec_os).l,8(a0) ; stuff saddr of GEM in PSP

pea (the_env).l ; our environment string

move.l a0,-(sp) ; push addr of PSP

pea nullenv(pc) ; null filename

move.w #4,-(sp) ; just-go

st_x: move.w #$4b,-(sp) ; function = exec

trap #1 ; do it

adda.w #14,sp ; cleanup stack

*+

* When startup fails (or if the exec returns,

* which "cannot happen") fake a system reset:

*-

jmp (reseth).l ; back to the beginning...

*+

* Default enviroment string

* Cannot be more than 20 chars long without modifying

* the declaration for the_env,

* Any char >= $80 terminates the string (and is included in it)

* The last '#' character is replaced by the boot drive's name (A, B, ...)

*-

orig_env: DC.B 'PATH=',0 ; default pathname

DC.B '#:\',0 ; is the boot device

DC.B $00 ; terminate env string

DC.B $ff ; end of the env string (for our copy)

cmdname: DC.B 'COMMAND.PRG',0 ; shell name

gemname: DC.B 'GEM.PRG',0 ; desktop name

DC.B 0

DC.B 0

setikbd: DC.B $80,$01

*+

* _dskboot - boot (or return diagnostics)

* Passed: nothing

* Returns: D0.W = error number (if nonzero)

*-

_dskboot: moveq #3,d0 ; %%3 ap cart

bsr cartscan

IF ROM_STBOOK

bsr cartscan_STBOOK_EXTROM

ENDIF

movea.l (hdv_boot).w,a0 ; go through boot vector

jsr (a0)

tst.w d0 ; any errors?

bne.s dskb1 ; (yes -- punt)

movea.l (_dskbufp).w,a0 ; a0 -> disk buffer

jsr (a0) ; execute boot sector (it might return)

dskb1: rts ; return status

mtest: move.l #80*200,d7 ; 80s

cmp.l (_hz_200).l,d7 ; is the system running for > 80s?

bcs dmaBoot ; (no memory test)

movea.w #0,a5 ; done status = false

mtestloop: cmpa.w #0,a5 ; memtest done?

bne mtest4 ; (yes)

bsr memtest

movea.w d0,a5 ; memtest done?

beq mtest5 ; (no)

move.w #$1b,-(sp)

move.l #$30002,-(sp)

trap #$d ; Bconout(2, ESC)

move.w #'p',4(sp)

move.l #$30002,(sp)

trap #$d ; Bconout(2, 'p') Reverse video

move.w #$1b,4(sp)

move.l #$30002,(sp)

trap #$d ; Bconout(2, ESC)

move.w #'w',4(sp)

move.l #$30002,(sp)

trap #$d ; Bconout(2, 'w') Discard end of line

move.l #200,d5 ; 200 = 1s

move.w #79,d4 ; 79

tst.b (sshiftmd).l

bne.s mtest2

move.l #2*200,d5 ; 2s

moveq #39,d4 ; 39

mtest2: move.l d5,d6

move.l d4,d3

mtestsp: move.w #' ',4(sp) ; d3 + 1 spaces

move.l #$30002,(sp)

trap #$d ; Bconout(2, ' ')

dbra d4,mtestsp

move.w #$d,4(sp)

move.l #$30002,(sp)

trap #$d ; Bconout(2, 13) CR

subq.l #1,d3

mtestsp2: move.w #' ',4(sp) ; d3 spaces

move.l #$30002,(sp)

trap #$d ; Bconout(2, ' ')

dbra d3,mtestsp2

move.w #$1b,4(sp)

move.l #$30002,(sp)

trap #$d ; Bconout(2, ESC)

move.w #'q',4(sp)

move.l #$30002,(sp)

trap #$d ; Bconout(2, 'q') Normal video

addq.l #6,sp

mtest4: cmp.l (_hz_200).l,d6

bhi.s mtest5

move.w #$1b,-(sp)

move.l #$30002,-(sp)

trap #$d ; Bconout(2, ESC)

move.w #'K',4(sp)

move.l #$30002,(sp)

trap #$d ; Bconout(2, 'K') Clear to eol

move.w #8,4(sp)

move.l #$30002,(sp)

trap #$d ; Bconout(2, 8) Backspace

addq.w #6,sp

add.l d5,d6

mtest5: cmpa.w #0,a5 ; memtest done?

beq.s mtest6 ; (no)

cmp.l (_hz_200).l,d7

bls.s mtest8

mtest6:

IF ROM_STBOOK

move.w (tt_mcu+4).l,d0

not.w d0

and.w #$c,d0 ; check bit 2 & 3

bne.s mtest7

ENDIF

move.l #$10002,-(sp)

trap #$d ; Bconstat(2) - key pressed?

addq.l #4,sp

tst.l d0

beq mtestloop ; (no - continue)

move.l #$20002,-(sp)

trap #$d ; Bconin(2) - read key

addq.l #4,sp

mtest7: cmpa.w #0,a5 ; memtest done?

bne.s mtest8 ; (yes)

bsr memtestabort

move.l d7,(_hz_200).l

bra.s dmaBoot

mtest8: move.l d7,(_hz_200).l

move.w #$d,-(sp)

move.l #$30002,-(sp)

trap #$d ; Bconout(2, 13) CR

move.w #$1b,4(sp)

move.l #$30002,(sp)

trap #$d ; Bconout(2, ESC)

move.w #'K',4(sp)

move.l #$30002,(sp)

trap #$d ; Bconout(2, 'K') Clear to eol

addq.l #6,sp

*--- boot from DMA device

dmaBoot:

IF ROM_STBOOK

clr.w (the_env).l ; index to the dmaDevList

ELIF ROM_TOS206

moveq #$10,d4

ELIF ROM_TOS306

jsr (_scsisubb).l

moveq #8,d4

move.b (scu_gp1).w,d0

and.w #$f8,d0

move.w d0,(defaultBootDevice).w

bne.s dmaBoot2

pea (defaultBootDevice).w

move.w #2,-(sp)

clr.l -(sp)

jsr (_NVMaccess).l

adda.w #$a,sp

tst.w d0

beq.s dmaBoot2

ENDIF

clr.w (defaultBootDevice).w

dmaBoot2: move.w #1,d1 ; d1 -> 2 tries per device

dmaBoot3: move.w d1,-(sp)

IF ROM_STBOOK

move.w (the_env).l,d4

move.b dmaDevList(pc,d4.w),d4

ENDIF

move.w d4,-(sp) ; pdev

move.l (_dskbufp).w,-(sp) ; buf = _dskbufp

move.w #1,-(sp) ; count = 1

clr.l -(sp) ; sectnum = 0

jsr (_dmaread).l ; read first sector of this device

adda.w #12,sp

move.w (sp)+,d1

tst.l d0 ; read successful?

beq.s dmaBoot4 ; yes ->

addq.l #1,d0 ; error == time out?

dbeq d1,dmaBoot3 ; timeout or another try left? ->

bra.s dmaexecl ; try next device

dmaBoot4: movea.l (_dskbufp).w,a0

move.w #$ff,d0 ; 256 word checksum over the boot sector

moveq #0,d1

dmaBoot5: add.w (a0)+,d1

dbra d0,dmaBoot5

cmp.w #$1234,d1 ; checksum == 0x1234?

beq.s dmaexec ; execute this valid boot sector ->

dmaexecl:

IF ROM_STBOOK

move.w (the_env).l,d4

addq.w #1,d4 ; increment next device

move.w d4,(the_env).l

cmpi.b #$ff,dmaDevList(pc,d4.w) ; end of the device list?

bne.s dmaBoot2 ; no -> continue with the next one

ELSE

addq.w #1,d4

move.w d4,d0

and.w #7,d0

bne.s dmaBoot2

cmp.w #8,d4

beq.s dmaBootx

moveq #0,d4

bra.s dmaBoot2

dmaBootx:

ENDIF

rts ; no valid boot sector found -> return

IF ROM_STBOOK

dmaDevList: DC.B $10,$11,$00,$01,$02,$03,$04,$05 ;boot order of DMA devices, $ff terminates the list

DC.B $06,$07,$ff

ENDIF

dmaexec: movea.l (_dskbufp).w,a0 ; pointer to the boot sector buffer

move.l #'DMAr',d3 ; d3 -> 'DMAr' magic

move.w d4,d7 ; d4 -> pdev

asl.w #5,d7 ; d7 = 0

move.w (defaultBootDevice).w,d5 ; defaultBootDevice = 0

IF !ROM_STBOOK

move.l d4,-(sp)

ENDIF

move.l (hdv_rw).l,-(sp) ; save read sector function pointer

jsr (a0) ; execute boot sector

move.l (sp)+,d0

IF !ROM_STBOOK

move.l (sp)+,d4

ENDIF

cmp.l (hdv_rw).w,d0 ; did the read sector function change?

beq.s dmaexecl ; no -> no device driver was loaded -> continue to load boot sectors

rts ; a new device driver was loaded -> return

*+

* cartscan - scan cartridge memory for runable applications

* Passed: d0 = bit# to test in application's initialization vector

* Returns: after all applications have been examined

* Uses: a0,d0

*-

IF ROM_STBOOK

cartscan_STBOOK_EXTROM:lea (STBOOK_EXTROM).l,a0

bra.s cartscan2

ENDIF